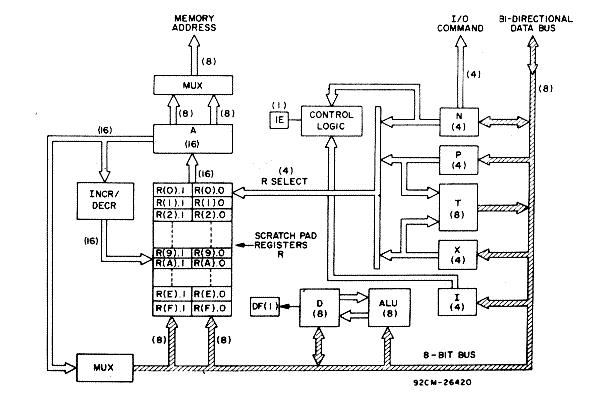

Fig. 7.41. Block diagram of the RCA COSMAC (Courtesy of RCA Solid State Division).

|

|

||

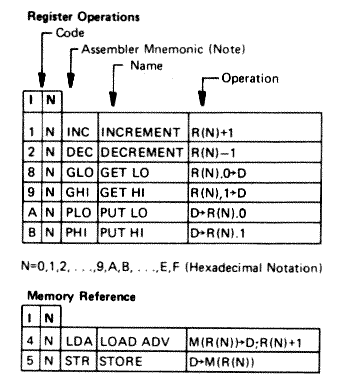

| Register | No. of Bits | Function |

|

|

||

| D | 8 | Data register (accumulator) |

| DF | 1 | Data flag (ALU carry) |

| R | 16 | 1-of-16 scratch-pad registers |

| P | 4 | Designates program counter R(P) |

| X | 4 | Designates data pointer R(X) |

| N | 4 | Low-order instruction digit |

| I | 4 | High-order instruction digit |

| T | 8 | Temporary register; holds old X and P after interrupt |

| IE | 1 | Interrupt enable |

|

|

||